PULSE GÜÇ KAYNAĞI GÜÇ ANAHTARI KONTROLÜ

TL494 ÜZERİNDEN

MAKALE A. V. GOLOVKOV ve V. B LYUBITSKY "SİSTEM MODÜLLERİ İÇİN GÜÇ KAYNAKLARI IBM PC-XT / AT" YAYINLANMASI "LAD ve N"

KONTROL DEVRESİ TL494

Modern UPS sistemlerinde, yüksek güçlü dönüştürücü transistörlerin kontrol anahtarlama voltajını oluşturmak için genellikle özel entegre devreler (IC'ler) kullanılır.

UPS'in normal olarak PWM modunda çalışması için ideal kontrol IC'si aşağıdaki koşulların çoğunu karşılamalıdır:

çalışma voltajı 40V'tan yüksek değil;

son derece kararlı, sıcaklık stabilize referans voltaj kaynağının varlığı;

testere dişi voltaj jeneratörünün varlığı

programlanabilir yumuşak başlatmanın harici bir sinyali ile senkronizasyon imkanı sağlamak;

yüksek ortak mod voltajına sahip bir uyumsuzluk sinyal yükselticisinin varlığı;

bir PWM karşılaştırıcısının varlığı;

darbe kontrollü bir tetikleyicinin varlığı;

kısa devre korumalı iki kanallı bir ön terminal kaskadının varlığı;

çift darbeyi bastırmak için mantığın varlığı;

çıkış voltajlarının simetrisini düzeltmek için araçların mevcudiyeti;

çok çeşitli ortak mod voltajlarında akım sınırlamasının yanı sıra acil modda kapatma ile her periyotta akım sınırlamasının varlığı;

doğrudan şanzımanlı otomatik kontrolün mevcudiyeti;

besleme gerilimi düştüğünde kapatmanın sağlanması;

aşırı gerilim koruması sağlamak;

TTL / CMOS mantığı ile uyumluluğun sağlanması;

uzaktan açma ve kapama sağlanması.

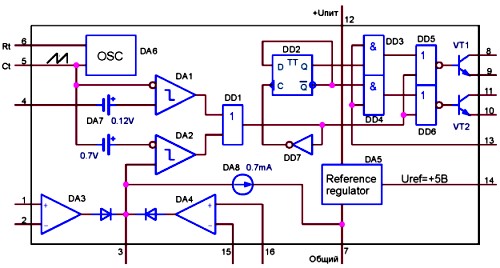

Şekil 11. TL494 kontrol mikro devresi ve pin çıkışı.

Vakaların ezici çoğunluğunda, TEXAS INSTRUMENT (ABD) tarafından üretilen bir TL494CN mikro devresi, dikkate alınan anahtarlamalı güç kaynakları sınıfı için bir kontrol devresi olarak kullanılır (Şekil 11). Yukarıdaki işlevlerin çoğunu uygular ve bir dizi yabancı şirket tarafından farklı isimler altında üretilir. Örneğin, SHARP (Japonya) IR3M02 mikro devresini üretir, FAIRCHILD (ABD) - UA494, SAMSUNG (Kore) - KA7500, FUJITSU (Japonya) - MB3759, vb. Tüm bu mikro devreler, ev tipi mikro devre KR1114EU4'ün tam analoglarıdır. Bu kontrol mikro devresinin yapısını ve çalışmasını ayrıntılı olarak ele alalım. KGK'nın güç bölümünü kontrol etmek için özel olarak tasarlanmıştır ve şunları içerir (Şekil 12):

Şekil 12. IC TL494'ün fonksiyonel şeması

DA6 testere dişi voltaj üreteci; GPN'nin frekansı, 5. ve 6. pinlere bağlı olan direnç ve kapasitörün değerleri ile belirlenir ve dikkate alınan güç kaynağı sınıfında yaklaşık 60 kHz'e eşit olarak seçilir;

harici çıkışlı (pim 14) referans stabilize voltaj kaynağı DA5 (Uref = + 5, OB);

karşılaştırıcı "ölü bölge" DA1;

karşılaştırıcı PWM DA2;

gerilim hatası yükselticisi DA3;

akım sınırlama sinyali DA4 için hata yükselticisi;

açık kollektörler ve emitörler ile iki çıkış transistörü VT1 ve VT2;

2 ile frekans bölme modunda dinamik itme-çekme D-tetiği - DD2;

yardımcı mantık kapıları DD1 (2-OR), DD3 (2nd), DD4 (2nd), DD5 (2-OR-NOT), DD6 (2-OR-NOT), DD7 (NOT);

0.1BDA7 dereceli sabit voltaj kaynağı;

0,7mA DA8 dereceli DC kaynağı.

Kontrol devresi başlayacaktır, yani. 8 ve 11 pinlerinde, seviyesi +7 ila +40 V aralığında olan pin 12'ye herhangi bir besleme voltajı uygulanırsa bir darbe dizisi görünecektir. TL494'ü oluşturan fonksiyonel birimlerin tamamı IC, koşullu olarak dijital ve analog kısma ayrılabilir (dijital ve analog sinyal yolları). Analog kısım, DA3, DA4, DA1, DA2 karşılaştırıcıları, testere dişi voltaj üreteci DA6 ve ayrıca DA5, DA7, DA8 yardımcı kaynaklarını içerir. Çıkış transistörleri dahil diğer tüm elemanlar dijital parçayı (dijital yol) oluşturur.

Şekil 13. IC TL494'ün nominal modda çalışması: U3, U4, U5 - 3, 4, 5 pinlerindeki voltajlar.

Dijital yolun çalışmasını en baştan ele alalım. Mikro devrenin çalışmasını açıklayan zamanlama diyagramları Şekil 2'de gösterilmektedir. 13. Zamanlama şemalarından, mikro devrenin çıkış kontrol darbelerinin görünüm anlarının ve bunların sürelerinin (şemalar 12 ve 13), mantık elemanı DD1'in (şema) çıkış durumu tarafından belirlendiği görülebilir. 5). "Mantık"ın geri kalanı, DD1 çıkış darbelerini iki kanala bölmenin yalnızca yardımcı bir işlevini yerine getirir. Bu durumda, mikro devrenin çıkış darbelerinin süresi, çıkış transistörleri VT1, VT2'nin açık durumunun süresi ile belirlenir. Bu transistörlerin her ikisi de açık kollektör ve emiterlere sahip olduğundan iki şekilde bağlanabilirler. Ortak bir yayıcı ile şemaya göre açıldığında, çıkış darbeleri transistörlerin harici toplayıcı yüklerinden (mikro devrenin 8 ve 11 pinlerinden) çıkarılır ve darbelerin kendileri pozitif seviyeden (önde gelen) aşağı doğru yönlendirilir. darbelerin kenarları negatiftir). Bu durumda transistörlerin yayıcıları (mikro devrenin 9 ve 10 numaralı pimleri) kural olarak topraklanır. Şemaya göre ortak bir toplayıcı ile açıldığında, transistörlerin yayıcılarına harici yükler bağlanır ve bu durumda yukarı doğru dalgalanmalarla yönlendirilen çıkış darbeleri (darbelerin ön kenarları pozitiftir) transistörlerin yayıcılarından çıkarılır. VT1, VT2. Bu transistörlerin toplayıcıları, kontrol mikro devresinin (Upom) güç veri yoluna bağlanır.

TL494 mikro devrenin dijital bölümünü oluşturan kalan işlevsel birimlerin çıkış darbeleri, mikro devre anahtarlama devresinden bağımsız olarak yukarı yönlü emisyonlardır.

Tetikleyici DD2, bir itme-çekme dinamik D-tetikleyicisidir. Çalışma prensibi aşağıdaki gibidir. DD1 elemanının çıkış darbesinin ön (pozitif) kenarında, DD2 flip-flop'un D girişinin durumu dahili kayıt defterine yazılır. Fiziksel olarak bu, DD2'de bulunan iki parmak arası terlikten ilkinin değiştirildiği anlamına gelir. DD1 elemanının çıkışındaki darbe sona erdiğinde, DD2'deki ikinci flip-flop bu darbenin takip eden (negatif) kenarında açılır ve DD2 çıkışlarının durumu değişir (D girişinden okunan bilgi Q çıkışında görünür ). Bu, bir periyot boyunca iki kez VT1, VT2 transistörlerinin her biri temelinde bir kilit açma darbesinin ortaya çıkma olasılığını ortadan kaldırır. Aslında, flip-flop DD2'nin C girişindeki darbe seviyesi değişmediği sürece, çıkışlarının durumu değişmeyecektir. Bu nedenle, darbe, örneğin üst kanal (DD3, DD5, VT1) gibi kanallardan biri aracılığıyla mikro devrenin çıkışına iletilir. C girişindeki darbe sona erdiğinde, DD2 tetiği değişir, üst kanalı kilitler ve alt kanalın kilidini açar (DD4, DD6, VT2). Bu nedenle, C girişine ve DD5, DD6 girişlerine gelen bir sonraki darbe, alt kanal aracılığıyla mikro devrenin çıkışına iletilecektir. Böylece, negatif kenarı olan DD1 elemanının çıkış darbelerinin her biri iki duraklı DD2'yi değiştirir ve böylece bir sonraki darbenin kanalını değiştirir. Bu nedenle, kontrol mikro devresi için referans malzeme, mikro devre mimarisinin bir çift darbenin bastırılmasını sağladığını gösterir, yani. periyot başına aynı transistöre dayalı iki kilit açma darbesinin görünümünü ortadan kaldırır.

Mikro devrenin dijital devresinin bir çalışma periyodunu ayrıntılı olarak ele alalım.

Üst (VT1) veya alt (VT2) kanalının çıkış transistörüne dayanan bir kilit açma darbesinin görünümü, DD5, DD6 ("2OR-NOT") elemanlarının mantığı ve DD3, DD4 ( "2-AND") öğeleri, sırayla DD2 tetikleyicisinin durumu tarafından belirlenir.

2-OR-NOT elemanının mantığı, bildiğiniz gibi, her ikisinde de düşük voltaj seviyeleri (mantıksal 0) varsa, böyle bir elemanın çıkışında yüksek seviyeli bir voltajın (mantıksal 1) görünmesidir. girdilerinden biridir. Giriş sinyallerinin diğer olası kombinasyonlarında, eleman 2 VEYA-NOT'un çıkışında bir düşük voltaj seviyesi (mantık 0) mevcuttur. Bu nedenle, DD2 tetikleyicisinin Q çıkışında mantıksal bir 1 (Şekil 13'teki diyagram 5'in ti momenti) ve çıkışında / Q - mantıksal bir 0 varsa, o zaman DD3 (2И) öğesinin her iki girişinde mantıksal 1 olacaktır ve bu nedenle, DD3 çıkışında ve dolayısıyla üst kanalın DD5 öğesinin (2OR-NOT) girişlerinden birinde mantıksal bir 1 görünecektir. Sonuç olarak, DD1 elemanının çıkışından bu elemanın ikinci girişine gelen sinyalin seviyesinden bağımsız olarak, DD5'in çıkışının durumu mantıksal O olacaktır ve transistör VT1 kapalı durumda kalacaktır. DD4 öğesinin çıkış durumu mantıksal 0 olacaktır, çünkü mantıksal 0, DD2 flip-flop'un / Q çıkışından gelen DD4 girişlerinden birinde bulunur. DD4 elemanının çıkışından gelen mantık 0, DD6 elemanının girişlerinden birine gider ve darbenin alt kanaldan geçmesine izin verir. Bu pozitif polarite darbesi (mantıksal 1) DD6'nın çıkışında ve dolayısıyla DD1 öğesinin çıkış darbeleri arasındaki duraklama süresi için VT2 temelinde görünecektir (yani, DD1'in çıkışının olduğu süre için). mantıksal bir 0 - Şekil 13'teki diyagram 5'in trt2 aralığı). Bu nedenle, transistör VT2 açılır ve toplayıcısında pozitif seviyeden aşağı doğru bir dalgalanma ile bir darbe belirir (ortak bir yayıcıya sahip bir devreye göre açma durumunda).

DD1 elemanının bir sonraki çıkış darbesinin başlangıcı (Şekil 13'teki diyagram 5'in t2 momenti), çıkışında bir DD6 elemanı hariç, mikro devrenin dijital yolunun elemanlarının durumunu değiştirmeyecektir. mantıksal 0 belirir ve bu nedenle transistör VT2 kapanacaktır. DD1 çıkış darbesinin (ta anı) tamamlanması, flip-flop DD2'nin çıkışlarının durumunda bir değişikliğe neden olacaktır (mantıksal 0 - Q çıkışında, mantıksal 1 - çıkış / Q'da). Bu nedenle, DD3, DD4 öğelerinin çıkışlarının durumu değişecektir (DD3 çıkışında - mantıksal 0, DD4 - mantıksal 1 çıkışında). 3 DD1 elemanının çıkışında başlayan duraklama, üst kanalın transistör VT1'ini açmayı mümkün kılacaktır. DD3 elemanının çıkışındaki mantık 0, bu olasılığı "doğrular" ve onu transistör VT1'e dayalı bir kilit açma darbesinin gerçek görünümüne dönüştürür. Bu dürtü, U anına kadar sürer, ardından VT1 kapanır ve işlemler tekrarlanır.

Bu nedenle, mikro devrenin dijital devresinin ana fikri, 8 ve 11 numaralı pinlerdeki (veya 9 ve 10 numaralı pinlerdeki) çıkış darbesinin süresinin, DD1'in çıkış darbeleri arasındaki duraklama süresi ile belirlenmesidir. öğe. DD3, DD4 elemanları, görünümü aynı eleman DD1 tarafından kontrol edilen flip-flop DD2'nin Q ve / Q çıkışlarında değişen düşük seviyeli bir sinyalde darbenin geçişi için kanalı belirler. DD5, DD6 öğeleri düşük seviyeli eşleştirme şemalarıdır.

Mikro devrenin işlevselliğinin tam bir açıklaması için, bir önemli özellik daha belirtilmelidir. Şeklin fonksiyonel diyagramından görülebileceği gibi, DD3, DD4 elemanlarının girişleri birleştirilir ve mikro devrenin 13 pimine getirilir. Bu nedenle, pim 13'e mantıksal bir 1 uygulanırsa, DD3, DD4 öğeleri, flip-flop DD2'nin Q ve / Q çıkışlarından gelen bilgilerin tekrarlayıcıları olarak çalışacaktır. Aynı zamanda, DD5, DD6 elemanları ve VT1, VT2 transistörleri, yarım periyotlu bir faz kayması ile anahtarlanacak ve bir itme-çekme yarım köprü devresine göre inşa edilmiş UPS'nin güç bölümünün çalışmasını sağlayacaktır. Pim 13'e mantıksal bir 0 uygulanırsa, DD3, DD4 öğeleri bloke edilir, yani. bu elemanların çıktılarının durumu değişmeyecektir (sabit mantık 0). Dolayısıyla DD1 elemanının çıkış darbeleri DD5, DD6 elemanları üzerinde aynı şekilde etki edecektir. DD5, DD6 öğeleri ve dolayısıyla VT1, VT2 çıkış transistörleri, faz kayması olmadan (aynı anda) geçiş yapacaktır. Kontrol mikro devresinin bu çalışma modu, UPS'in güç bölümü tek çevrimli bir devreye göre yapılmışsa kullanılır. Bu durumda, mikro devrenin her iki çıkış transistörünün toplayıcıları ve emitörleri, güç sağlamak için birleştirilir.

Çıkış voltajı, itme-çekme devrelerinde "sert" bir mantıksal birim olarak kullanılır.

Uref mikro devresinin dahili kaynağı (mikro devrenin pim 13'ü pim 14 ile birleştirilir).

Şimdi mikro devrenin analog devresinin çalışmasına bakalım.

DD1 çıkışının durumu, DD1 girişlerinden birine ulaşan PWM DA2 karşılaştırıcısının (şema 4) çıkış sinyali ile belirlenir. DD1'in ikinci girişine sağlanan DA1 karşılaştırıcısının (şema 2) çıkış sinyali, normal çalışmada PWM karşılaştırıcı DA2'nin daha geniş çıkış darbeleri tarafından belirlenen DD1 çıkışının durumunu etkilemez.

Ek olarak, Şekil 13'teki şemalardan, PWM karşılaştırıcısının (şema 3) ters çevirmeyen girişindeki voltaj seviyesindeki değişikliklerle, mikro devrenin çıkış darbelerinin genişliğinin (şema 12, 13) görülebileceği görülebilir. ) orantılı olarak değişecektir. Normal çalışmada, PWM karşılaştırıcı DA2'nin evirmeyen girişindeki voltaj seviyesi, yalnızca DA3 hata amplifikatörünün çıkış voltajı tarafından belirlenir (çünkü DA4 amplifikatörünün çıkış voltajını aşıyor), bu da seviyenin seviyesine bağlıdır. ters çevirmeyen girişinde geri besleme sinyali (mikro devrenin 1. pimi). Bu nedenle, mikro devrenin pim 1'ine bir geri besleme sinyali uygulandığında, çıkış kontrol darbelerinin genişliği, bu geri besleme sinyalinin seviyesindeki değişiklikle orantılı olarak değişecek ve bu da, sırayla, değişikliklerle orantılı olarak değişecektir. UPS çıkış voltajının seviyesi, çünkü geri bildirim oradan başlar.

Hem çıkış transistörleri VT1 hem de VT2 kapalıyken, mikro devrenin 8 ve 11 pinlerindeki çıkış darbeleri arasındaki zaman aralıklarına "ölü bölgeler" denir.

DA1 karşılaştırıcısına "ölü bölge" karşılaştırıcısı denir çünkü mümkün olan minimum süresini tanımlar. Bunu daha ayrıntılı olarak açıklayalım.

Şekil 13'teki zamanlama şemalarından, herhangi bir nedenle PWM karşılaştırıcı DA2'nin çıkış darbelerinin genişliği azalırsa, bu darbelerin belirli bir genişliğinden başlayarak, DA1 karşılaştırıcısının çıkış darbelerinin, çıkış darbelerinin daha geniş olacağı izler. PWM karşılaştırıcı DA2'nin çıkış darbeleri ve mantıksal eleman DD1'in çıktısının durumunu belirlemeye başlar ve dolayısıyla. mikro devrenin çıkış darbelerinin genişliği. Başka bir deyişle, DA1 karşılaştırıcısı, mikro devrenin çıkış darbe genişliğini belirli bir maksimum seviyeye sınırlar. Sınırlayıcı seviye, sabit durumda DA1 karşılaştırıcısının (mikro devrenin pim 4) evirmeyen girişindeki potansiyel tarafından belirlenir. Bununla birlikte, diğer yandan, pim 4'teki potansiyel, mikro devrenin çıkış darbelerinin enlem ayar aralığını belirleyecektir. Pim 4'te artan potansiyel ile bu aralık daralır. En geniş ayar aralığı, pim 4'teki potansiyel 0 olduğunda elde edilir.

Ancak bu durumda, "ölü bölge" genişliğinin 0'a eşit olabileceği gerçeğiyle ilişkili bir tehlike vardır (örneğin, UPS'ten çekilen akımın önemli bir artışı durumunda). Bu, mikro devrenin 8 ve 11 pinlerindeki kontrol darbelerinin birbiri ardına doğrudan takip edeceği anlamına gelir. Bu nedenle "sütun kırılması" olarak bilinen bir durum ortaya çıkabilir. İnvertörün güç transistörlerinin anında açılıp kapanamayan ataleti ile açıklanmaktadır. Bu nedenle, aynı anda daha önce açılmış transistörün tabanına bir engelleme sinyali ve kapalı transistörün tabanına bir kilit açma sinyali (yani sıfır "ölü bölge" ile) uygulanırsa, o zaman bir durum ortaya çıkacaktır. bir transistör henüz kapanmadığında ve diğeri zaten açıkken. Daha sonra, her iki transistörden geçen akımın akışından oluşan yarım köprünün transistör rafı boyunca bir arıza meydana gelir. Bu akım, Şekil 2'deki diyagramdan görülebileceği gibi. 5, güç transformatörünün birincil sargısını atlar ve pratik olarak sınırsızdır. Bu durumda akım koruma çalışmaz, çünkü akım, akım sensöründen geçmez (şemada gösterilmemiştir; kullanılan akım sensörlerinin tasarımı ve çalışma prensibi sonraki bölümlerde ayrıntılı olarak tartışılacaktır), yani bu sensör kontrole sinyal gönderemez devre. Bu nedenle, geçiş akımı çok kısa sürede çok yüksek bir değere ulaşır. Bu, her iki güç transistöründe serbest bırakılan güçte keskin bir artışa ve neredeyse anlık arızalarına (kural olarak, arıza) yol açar. Ek olarak, güç doğrultucu köprüsünün diyotları, geçen akımın ani akımından zarar görebilir. Bu işlem, ataleti nedeniyle devre elemanlarını korumak için zamana sahip olmayan, ancak yalnızca birincil ağı aşırı yükten koruyan yanmış bir ağ sigortası ile sona erer.

Bu nedenle kontrol gerilimi; Güç transistörlerinin tabanlarına beslenen transistörler, bu transistörlerden ilki güvenilir bir şekilde kapanacak ve ancak o zaman diğeri açılacak şekilde oluşturulmalıdır. Başka bir deyişle, güç transistörlerinin tabanlarına uygulanan kontrol darbeleri arasında mutlaka sıfıra eşit olmayan bir zaman kayması ("ölü bölge") olmalıdır. "Ölü bölge"nin izin verilen minimum süresi, güç anahtarları olarak kullanılan transistörlerin ataleti ile belirlenir.

Mikro devrenin mimarisi, mikro devrenin pim 4'ündeki potansiyeli kullanarak "ölü bölgenin" minimum süresinin değerini ayarlamanıza izin verir. Bu potansiyel, Uref mikro devresinin dahili referans kaynağının çıkış voltajı barasına bağlı bir harici bölücü kullanılarak ayarlanır.

Bazı UPS sürümlerinde böyle bir ayırıcı yoktur. Bu, yumuşak başlatma işleminin tamamlanmasından sonra (aşağıya bakınız), mikro devrenin pim 4'ündeki potansiyelin 0 olacağı anlamına gelir. Bu durumlarda, "ölü bölge"nin mümkün olan minimum süresi hala 0 olmayacak, ancak pozitif kutbu ile karşılaştırıcı DA1'in ters çevirmeyen girişine ve mikro devrenin negatif pin 4'üne bağlı olan dahili voltaj kaynağı DA7 (0, 1B) tarafından belirlenir. Bu nedenle, bu kaynağın dahil edilmesi nedeniyle, karşılaştırıcı DA1'in çıkış darbesinin genişliği ve dolayısıyla "ölü bölgenin" genişliği hiçbir koşulda 0'a eşit olamaz, bu da "raf boyunca bozulma" anlamına gelir. temelde imkansız olacaktır. Başka bir deyişle, mikro devrenin mimarisi, çıkış darbesinin maksimum süresinin ("ölü bölgenin" minimum süresi) bir sınırlamasını içerir. Mikro devrenin pim 4'üne bağlı bir bölücü varsa, yumuşak bir başlangıçtan sonra, bu pimin potansiyeli 0 değildir, bu nedenle DA1 karşılaştırıcısının çıkış darbelerinin genişliği yalnızca dahili kaynak DA7 tarafından değil, aynı zamanda belirlenir. ayrıca pim 4'teki artık (yumuşak başlatma işleminin tamamlanmasından sonra) potansiyel ile. Ancak aynı zamanda, yukarıda bahsedildiği gibi, PWM karşılaştırıcı DA2'nin genişlik ayarının dinamik aralığı daralır.

BAŞLANGIÇ ŞEMASI

Başlatma devresi, IVP'yi besleme ağına açtıktan sonra başlatmak için kontrol mikro devresine güç verebilecek bir voltaj elde etmek üzere tasarlanmıştır. Bu nedenle, başlatma, normal çalışması olmadan, güç ünitesinin ve tüm UPS devresinin bir bütün olarak çalışmasının imkansız olduğu ilk etapta kontrol mikro devresinin başlatılması anlamına gelir.

Başlangıç devresi iki farklı şekilde oluşturulabilir:

kendinden heyecanlı;

zorla heyecanla.

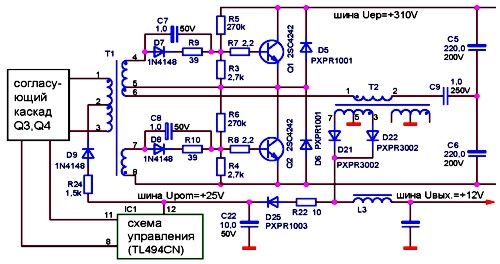

Örneğin GT-150W UPS'de kendinden enerjili bir devre kullanılır (Şekil 14). Doğrultulmuş şebeke gerilimi Uep, her iki güç anahtarı transistör Q1, Q2 için temel olan dirençli bölücü R5, R3, R6, R4'e beslenir. Bu nedenle, transistörler aracılığıyla, C5, C6 (Uep) kapasitörleri üzerindeki toplam voltajın etkisi altında, baz akım devreden akmaya başlar (+) C5 - R5 - R7 - 6. Q1 - R6 - R8 - 6. Q2 - birincil tarafın "ortak teli" - (-) C6.

Her iki transistör de bu akım tarafından açılır. Sonuç olarak, karşılıklı olarak zıt yönlerdeki akımlar, her iki transistörün kollektör-verici bölümlerinden devreler boyunca akmaya başlar:

Q1 aracılığıyla: (+) C5 - veri yolu +310 V - to-e Q1 - 5-6 T1 -1-2 T2-C9- (-) C5.

Q2 aracılığıyla: (+) C6 - C9 - 2-1 T2 - 6-5 T1 - to-e Q2 - birincil tarafın "ortak kablosu" - (-) C6.

Şekil 14. GT-150W UPS'nin kendinden enerjili başlatma şeması.

Ek (başlangıç) 5-6 T1 dönüşlerinden zıt yönlerde akan her iki akım da eşit olsaydı, ortaya çıkan akım 0 olur ve devre başlayamazdı.

Bununla birlikte, Q1, Q2 transistörlerinin akım yükseltme faktörlerinin teknolojik olarak yayılması nedeniyle, bu akımlardan biri her zaman diğerinden daha büyüktür, çünkü transistörler değişen derecelerde biraz açıktır. Bu nedenle, 5-6 T1 dönüşlerinden elde edilen akım 0'a eşit değildir ve bir yöne veya diğerine sahiptir. Q1 transistöründen geçen akımın baskın olduğunu (yani, Q1'in Q2'den biraz daha açık olduğunu) ve dolayısıyla akımın T1'in pim 5'ten pim 6'ya doğru aktığını varsayalım. Daha fazla akıl yürütme bu varsayıma dayanmaktadır.

Bununla birlikte, adil olmak gerekirse, transistör Q2'den geçen akımın da geçerli olabileceği ve daha sonra aşağıda açıklanan tüm işlemlerin transistör Q2'ye atıfta bulunacağı belirtilmelidir.

5-6 T1 dönüşlerinden geçen akımın akışı, kontrol transformatörü T1'in tüm sargılarında karşılıklı indüksiyon EMF'sinin ortaya çıkmasına neden olur. Bu durumda, (+) EMF, pim 5'e göre pim 4'te meydana gelir ve bu EMF'nin etkisi altında, devre üzerinden Q1: 4 T1 - D7-R9-R7-6-3'ün tabanına ek bir akım akar. Q1 - 5 T1.

Aynı zamanda (-) EMF, pim 8'e göre T1'in pim 7'sinde görünür, yani. bu EMF'nin polaritesinin Q2 için bloke olduğu ortaya çıkıyor ve kapanıyor. Ardından olumlu geribildirim (PIC) devreye girer. Eylemi, Q1 toplayıcı-verici bölümü boyunca akımın artması ve 5-6 T1 dönüşünün artmasıyla, artan bir EMF'nin 4-5 T1 sargısına etki etmesi ve bu da Q1 için ek bir baz akımı oluşturması gerçeğinde yatmaktadır. daha da fazla. Bu süreç bir çığ gibi (çok hızlı) gelişir ve Q1'in tamamen açılmasına ve Q2'nin kilitlenmesine yol açar. Güç darbe transformatörü T2'nin açık Q1 ve birincil sargısı 1-2 boyunca, doğrusal olarak artan bir akım akmaya başlar, bu da T2'nin tüm sargılarında karşılıklı endüksiyonlu bir EMF darbesinin ortaya çıkmasına neden olur. 7-5 T2 sargısından gelen bir darbe, C22 depolama kapasitörünü şarj eder. C22'de TL494 tipi kontrol IC1'inin 12 pinine ve eşleştirme aşamasına güç kaynağı olarak sağlanan bir voltaj belirir. Mikro devre başlar ve terminallerinde 11, 8 dikdörtgen darbe dizisi üretir, bu da eşleştirme aşaması (Q3, Q4, T1) aracılığıyla Q1, Q2 güç anahtarlarını değiştirmeye başlar. Nominal seviyenin darbe EMF'si, güç trafosu T2'nin tüm sargılarında görünür. Bu durumda, 3-5 ve 7-5 sargılarından gelen EMF, üzerinde sabit bir voltaj seviyesini koruyarak (yaklaşık + 27V) sürekli olarak C22'yi besler. Başka bir deyişle, mikro devre, geri besleme döngüsü (kendi kendine besleme) boyunca kendini beslemeye başlar. Ünite çalışma moduna girer. Mikro devrenin besleme voltajı ve eşleştirme aşaması yardımcıdır, yalnızca ünite içinde hareket eder ve genellikle Upom olarak adlandırılır.

Bu devre, Mazovia CM1914 bilgisayarı için LPS-02-150XT anahtarlamalı güç kaynağı (Tayvan'da üretilmiştir) gibi bazı varyasyonlara sahip olabilir (Şekil 15). Bu devrede, başlatma işleminin gelişimi için ilk itici güç, güç anahtarları için temel olan dirençli bölücüyü ilk pozitif yarım döngüde besleyen ayrı bir yarım dalga doğrultucu D1, C7 yardımı ile elde edilir. ağın. Bu, başlatma sürecini hızlandırır çünkü Anahtarlardan birinin ilk kilidinin açılması, büyük kapasiteli yumuşatma kapasitörlerinin şarj edilmesine paralel olarak gerçekleşir. Planın geri kalanı yukarıda tartışıldığı gibi çalışır.

Şekil 15. LPS-02-150XT anahtarlamalı güç kaynağında kendi kendine uyarma başlatma devresi

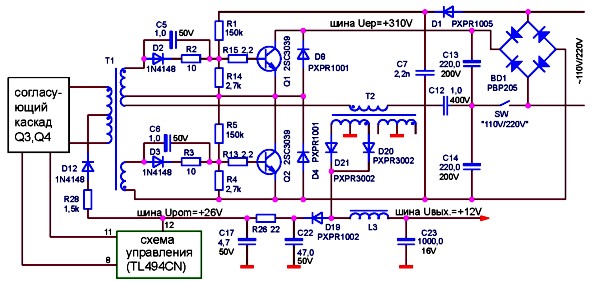

Böyle bir şema, örneğin, LING YIN GROUP (Tayvan) tarafından PS-200B UPS'de kullanılır.

Özel başlatma transformatörü T1'in birincil sargısı, şebeke voltajının yarısında (220V nominal değerde) veya tam (110V nominal değerde) açılır. Bu, T1'in sekonder sargısındaki alternatif voltajın genliğinin besleme şebekesinin derecesine bağlı olmayacağı dikkate alınarak yapılır. UPS açıldığında, T1'in birincil sargısından alternatif bir akım akar. İkincil sargı 3-4 T1'de, bu nedenle, besleme ağının frekansı ile alternatif bir sinüzoidal EMF indüklenir. Bu EMF'nin etkisi altında akan akım, D3-D6 diyotları üzerindeki özel bir köprü devresi ile doğrultulur ve bir kapasitör C26 ile düzleştirilir. C26'da, TL494 tipi kontrol mikro devresi U1'in 12 pimine ve eşleştirme aşamasına güç kaynağı olarak sağlanan yaklaşık 10-11V'luk sabit bir voltaj tahsis edilir. Bu işleme paralel olarak yumuşatma filtresinin kapasitörleri şarj edilir. Bu nedenle, mikro devreye güç uygulandığında, güç aşamasına da güç verilir. Mikro devre başlar ve 8, 11 çıkışlarında, güç anahtarlarının eşleştirme aşamasından geçmeye başladığı bir dizi dikdörtgen darbe üretmeye başlar. Sonuç olarak, bloğun çıkış voltajları görünür. Kendinden besleme moduna girdikten sonra, mikro devre, D8 ayırma diyotu aracılığıyla + 12V çıkış voltajı barasından üretilir. Bu kendi kendini besleyen voltaj, D3-D5 doğrultucunun çıkış voltajını biraz aştığından, bu başlangıç doğrultucusunun diyotları kilitlenir ve devrenin çalışmasını daha fazla etkilemez.

D8 diyotu aracılığıyla geri bildirim ihtiyacı isteğe bağlıdır. Zorlanmış uyarma kullanan bazı UPS devrelerinde böyle bir bağlantı yoktur. Kontrol mikro devresi ve eşleştirme aşaması, tüm çalışma süresi boyunca başlangıç redresörünün çıkışından güç alır. Bununla birlikte, bu durumda Upom veriyolundaki dalgalanma seviyesinin, mikro devreye + 12V çıkış voltajı veriyolundan güç verilmesi durumundan biraz daha yüksek olduğu ortaya çıkıyor.

Fırlatma planlarının açıklamasını özetleyerek, yapılarının ana özelliklerini not edebiliriz. Kendinden tahrikli bir devrede, güç transistörlerinin ilk geçişi gerçekleştirilir ve bu, Upom mikro devresinin besleme voltajının ortaya çıkmasına neden olur. Zorlanmış uyarımlı bir şemada ilk önce Upom elde edilir ve sonuç olarak güç transistörlerinin anahtarlanması elde edilir. Ayrıca kendinden tahrikli devrelerde Upom gerilimi genellikle +26V civarında, cebri ikaz devrelerinde ise +12V civarındadır.

Zorlanmış uyarma (ayrı bir transformatör ile) Şekil 16'da gösterilmiştir.

Şekil 16. PS-200B anahtarlamalı güç kaynağının (LING YIN GRUBU) zorunlu uyarılmasıyla başlatma şeması.

PULS GÜÇ KAYNAĞI BAĞLANTI AŞAMASI

Düşük güçlü kontrol devrelerinden güçlü bir çıkış aşamasını eşleştirmek ve izole etmek için bir eşleştirme aşaması kullanılır.

Çeşitli UPS'lerde eşleşen bir kademeli oluşturmak için pratik şemalar iki ana seçeneğe ayrılabilir:

harici ayrık transistörlerin anahtar olarak kullanıldığı transistör versiyonu;

kontrol mikro devresinin çıkış transistörlerinin kendisinin VT1, VT2 (entegre versiyonda) anahtar olarak kullanıldığı transistörsüz versiyon.

Ek olarak, eşleştirme aşamalarının sınıflandırılabileceği bir diğer özellik, yarım köprü inverterin güç transistörlerinin kontrol edilme şeklidir. Bu temelde, tüm eşleştirme aşamaları şu şekilde ayrılabilir:

her iki güç transistörünün bir birincil ve iki ikincil sargıya sahip bir ortak kontrol transformatörü kullanılarak kontrol edildiği ortak kontrollü kaskadlar;

Güç transistörlerinin her birinin ayrı bir transformatör kullanılarak kontrol edildiği, ayrı kontrollü kaskadlar, yani. eşleştirme aşaması iki kontrol transformatörüne sahiptir.

Her iki sınıflandırmaya göre eşleştirme aşaması dört yoldan biriyle gerçekleştirilebilir:

ortak kontrollü transistör;

ayrı kontrollü transistör;

ortak kontrollü transistörsüz;

ayrı kontrol ile transistörsüz.

Ayrı ayrı kontrol edilen transistör kademeleri nadiren kullanılır veya hiç kullanılmaz. Yazarların, eşleşen kademeli yürütmenin böyle bir çeşidine rastlama şansı yoktu. Diğer üç seçenek az çok yaygındır.

Tüm versiyonlarda, güç aşaması ile iletişim trafo şeklinde gerçekleştirilir.

Bu durumda, transformatör iki ana işlevi yerine getirir: kontrol sinyalinin akımla yükseltilmesi (gerilim tarafından zayıflama nedeniyle) ve galvanik izolasyon. Kontrol IC ve eşleştirme aşaması ikincil tarafta ve güç aşaması KGK'nın birincil tarafında olduğundan galvanik izolasyon gereklidir.

Eşleştirme aşamasının belirtilen varyantlarının her birinin çalışmasını belirli örnekler kullanarak ele alalım.

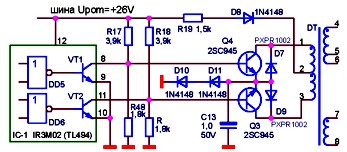

Ortak kontrol transistör devresinde, Q3 ve Q4 transistörlü bir itme-çekme transformatörü ön yükselticisi, eşleştirme aşaması olarak kullanılır (Şekil 17).

Şekil 17. KYP-150W anahtarlamalı güç kaynağının (ortak kontrollü transistör devresi) eşleştirme aşaması.

Şekil 18. Kollektörlerdeki gerçek darbeler

DT çekirdeğinde depolanan manyetik enerjinin etkisi altında akan D7 ve D9 diyotlarından geçen akımlar, düşen bir üstel şeklindedir. DT çekirdeğinde, akımların D7 ve D9 diyotlarından akışı sırasında, ikincil sargılarında EMF darbelerinin ortaya çıkmasına neden olan değişen (azalan) bir manyetik akı hareket eder.

Diode D8, ortak güç veriyolu aracılığıyla kontrol mikro devresi üzerindeki eşleştirme aşamasının etkisini ortadan kaldırır.

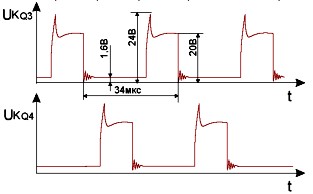

ESAN ESP-1003R anahtarlamalı güç kaynağında ortak kontrollü başka bir transistör eşleştirme aşaması türü kullanılmaktadır (Şekil 19). Bu seçeneğin ilk özelliği, mikro devrenin çıkış transistörleri VT1, VT2'nin emitör takipçileri olarak dahil edilmesidir. Çıkış sinyalleri, mikro devrenin 9, 10 numaralı pinlerinden alınır. Dirençler R17, R16 ve R15, R14, sırasıyla VT1 ve VT2 transistörlerinin yayıcı yükleridir. Aynı dirençler, anahtar modunda çalışan Q3, Q4 transistörleri için temel bölücüleri oluşturur. C13 ve C12 kapasiteleri, Q3, Q4 transistörlerinin anahtarlama işlemlerini zorlar ve hızlandırır. Bu aşamanın ikinci karakteristik özelliği, kontrol transformatörü DT'nin birincil sargısının orta noktadan çıkış olmaması ve Q3, Q4 transistörlerinin kollektörleri arasına bağlanmasıdır. Kontrol mikro devresinin çıkış transistörü VT1 açıldığında, transistör Q3 için temel olan bölücü R17, R16 olan Upom voltajı tarafından çalıştırıldığı ortaya çıkıyor. Bu nedenle, Q3 kontrol bağlantısından bir akım akar ve açılır. Bu işlemin hızlandırılması, sabit durum değerinden 2-2,5 kat daha yüksek olan Q3'ün tabanına bir kilit açma akımı beslemesi sağlayan zorlama kapasitansı C13 tarafından kolaylaştırılır. Q3'ün açılmasının sonucu, birincil sargı 1-2 DT'nin pim 1 ile kasaya bağlanmasıdır. İkinci transistör Q4 kilitlendiğinden, devre boyunca birincil sargı DT üzerinden artan bir akım akmaya başlar: Upom - R11 - 2-1 DT - to-e Q3 - durumda.

Şekil 19. ESP-1003R ESAN ELECTRONIC CO., LTD anahtarlamalı güç kaynağının (ortak kontrol transistör devresi) eşleşme aşaması.

3-4 ve 5-6 DT ikincil sargılarında, dikdörtgen şeklindeki EMF darbeleri görünür. DT sekonder sargılarının sarım yönü farklıdır. Bu nedenle, güç transistörlerinden biri (şemada gösterilmemiştir) bir açılış baz darbesi ve diğeri - bir kapanış alacaktır. Kontrol mikro devresinin VT1'i aniden kapandığında, ardından Q3 de aniden kapanır. Kapatma işleminin hızlandırılması, gerilimin, kapatma polaritesinde Q3 baz-yayıcı bağlantısına uygulanan zorlama kapasitansı C13 ile kolaylaştırılır. Ardından, mikro devrenin her iki çıkış transistörü kapatıldığında "ölü bölge" sürer. Ardından, çıkış transistörü VT2 açılır, bu, ikinci transistör Q4 için taban bölücü R15, R14'ün Upom voltajı tarafından çalıştırıldığı anlamına gelir. Bu nedenle, Q4 açılır ve birincil sargı 1-2 DT'nin diğer ucuyla (pim 2) kasaya bağlı olduğu ortaya çıkar, bu nedenle, devre boyunca önceki duruma zıt yönde artan bir akım akmaya başlar. : Upom -R10- 1-2 DT - to-e Q4 - "çerçeve".

Bu nedenle, ikincil sargılar DT üzerindeki darbelerin polaritesi değişir ve açılış darbesi ikinci güç transistörü tarafından alınacak ve birincisinin temelinde bir kapanma polaritesi darbesi hareket edecektir. Kontrol mikro devresinin VT2'si aniden kapandığında, Q4 de ondan sonra aniden kapanır (zorlama kapasitansı C12'nin yardımıyla). Ardından "ölü bölge" tekrar devam eder, ardından işlemler tekrarlanır.

Bu nedenle, bu kaskadın çalışmasının arkasındaki ana fikir, DT primer sargısının kasaya bir veya diğer uçtan bağlanması nedeniyle DT çekirdeğindeki değişken manyetik akı elde edilebilmesidir. Bu nedenle, tek kutuplu bir güç kaynağına sahip sabit bir bileşen olmadan alternatif bir akım içinden geçer.

UPS'in eşleştirme aşamalarının transistörsüz versiyonlarında, kontrol mikro devresinin çıkış transistörleri VT1, VT2, daha önce belirtildiği gibi eşleştirme aşamasının transistörleri olarak kullanılır. Bu durumda, ayrık eşleşen transistörler yoktur.

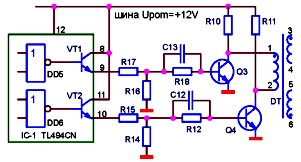

Örneğin, PS-200V UPS devresinde ortak kontrol transistörsüz devresi kullanılır. Mikro devre VT1, VT2'nin çıkış transistörleri, DT transformatörünün birincil yarı sargıları tarafından kollektörler boyunca yüklenir (Şekil 20). Güç, birincil sargı DT'nin orta noktasına sağlanır.

Şekil 20. PS-200B anahtarlamalı güç kaynağının (ortak kontrollü transistörsüz devre) eşleştirme aşaması.

Transistör VT1 açıldığında, artan akım bu transistörden ve kontrol transformatörü DT'nin 1-2 yarım sargısından akar. Sekonder sargılarda DT, kontrol darbeleri öyle bir polaritede görünür ki, inverterin güç transistörlerinden biri açılır ve diğeri kapanır. Darbenin sonunda, VT1 aniden kapanır, 1-2 DT yarım sargıdan geçen akım durur, bu nedenle ikincil sargılar DT üzerindeki EMF kaybolur, bu da güç transistörlerinin kapanmasına yol açar. Ayrıca, "ölü bölge", mikro devrenin her iki çıkış transistörü VT1, VT2 kapatıldığında ve akım birincil sargı DT üzerinden akmadığında sürer. Daha sonra transistör VT2 açılır ve zamanla artan akım bu transistörden ve 2-3 DT yarım sargıdan akar. Çekirdek DT'de bu akımın yarattığı manyetik akı, önceki durumun tersi yöndedir. Bu nedenle, ikincil sargılarda DT, önceki durumda zıt kutuplu bir EMF indüklenir. Sonuç olarak, yarım köprü invertörün ikinci transistörü açılır ve ilk darbenin temelinde bir kapanış polaritesi bulunur. Kontrol mikro devresinin VT2'si kapandığında, içinden geçen akım ve DT'nin birincil sargısı durur. Bu nedenle, DT sekonder sargılarındaki EMF kaybolur ve invertörün güç transistörleri tekrar kapanır. Ardından "ölü bölge" tekrar devam eder ve ardından işlemler tekrarlanır.

Bu aşamayı kurmanın ana fikri, kontrol transformatörünün çekirdeğindeki alternatif manyetik akının, bu transformatörün birincil sargısının orta noktasına güç sağlanarak elde edilebilmesidir. Bu nedenle, akımlar farklı yönlerde aynı sayıda dönüşle yarım sargılardan akar. Mikro devrenin her iki çıkış transistörü kapatıldığında ("ölü bölgeler"), çekirdek DT'deki manyetik akı 0'a eşittir. Transistörlerin alternatif açılması, bir veya diğer yarım sargının manyetik akısının alternatif görünümüne neden olur. . Çekirdekte ortaya çıkan manyetik akı değişkendir.

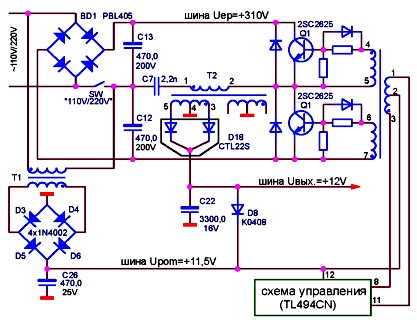

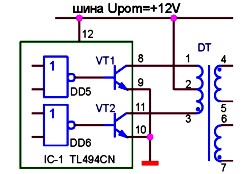

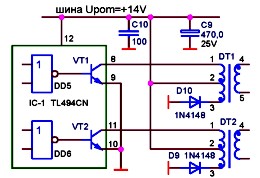

Bu tiplerin sonuncusu (ayrı kontrollü transistörsüz devre), örneğin Appis bilgisayarının (Peru) UPS'inde kullanılır. Bu devrede, birincil yarı sargıları mikro devrenin çıkış transistörleri için kollektör yükleri olan iki kontrol transformatörü DT1, DT2 vardır (Şekil 21). Bu şemada, iki güç anahtarının her biri ayrı bir transformatör aracılığıyla kontrol edilir. Mikro devrenin çıkış transistörlerinin toplayıcılarına, DT1, DT2 kontrol transformatörlerinin birincil sargılarının orta noktaları aracılığıyla ortak Upom veriyolundan güç sağlanır.

D9, D10 diyotları, birincil sargıların DT1, DT2 karşılık gelen parçaları ile çekirdek manyetik giderme devrelerini oluşturur. Bu konu üzerinde daha ayrıntılı olarak duralım.

Şekil 21. "Appis" anahtarlamalı güç kaynağının eşleştirme aşaması (ayrı kontrollü transistörsüz devre).

Eşleştirme aşaması (Şekil 21) esasen iki bağımsız tek uçlu ileri dönüştürücüdür, çünkü açılış akımı, eşleşen transistörün açık durumu sırasında güç transistörünün tabanına akar, yani. Eşleştirme ve ona bir transformatör aracılığıyla bağlanan güç transistörü aynı anda açılır. Bu durumda, her iki darbe transformatörü DT1, DT2, birincil sargı akımının sabit bir bileşeni ile çalışır, yani. zorla önyargı ile. Çekirdekleri manyetiklikten arındırmak için özel bir önlem alınmazsa, birkaç dönüştürücü çalışma süresi boyunca manyetik doygunluğa girecekler ve bu, birincil sargıların endüktansında önemli bir azalmaya ve VT1, VT2 anahtarlama transistörlerinin arızalanmasına yol açacaktır. Transistör VT1 ve transformatör DT1 üzerindeki dönüştürücüde gerçekleşen işlemleri düşünün. Transistör VT1 açıldığında, içinden doğrusal olarak artan bir akım akar ve 1-2 DT1 birincil sargısı devreden geçer: Upom -2-1 DT1 - to-e VT1 - "kasa".

VT1'in tabanındaki kilit açma darbesi sona erdiğinde aniden kapanır. 1-2 DT1 sargısından geçen akım durur. Bununla birlikte, 2-3 DT1 demanyetize edici sargı üzerindeki EMF, polaritesini değiştirir ve bu sargı ve D10 diyotu aracılığıyla, DT1 demanyetize edici çekirdek devreden akar: 2 DT1 - Upom - C9- "kasa" - D10-3DT1.

Bu akım lineer olarak azalmaktadır, yani. DT1 çekirdeğinden geçen manyetik akının türevi işaret değiştirir ve çekirdeğin manyetikliği giderilir. Böylece, bu ters çevrim sırasında, VT1 transistörünün açık durumu sırasında DT1 çekirdeğinde depolanan fazla enerji kaynağa geri döndürülür (Upom veri yolunun depolama kapasitörü C9 yeniden şarj edilir).

Ancak, eşleştirme aşamasının bu uygulaması en az tercih edilendir, çünkü her iki transformatör DT1, DT2 endüksiyon yetersiz kullanımı ve birincil sargı akımının sabit bir bileşeni ile çalışır. DT1, DT2 çekirdeklerinin manyetizasyonu, yalnızca pozitif endüksiyon değerlerini kapsayan özel bir döngüde gerçekleşir. Bu nedenle, çekirdeklerdeki manyetik akılar titreşir, yani. sabit bir bileşen içerir. Bu, DT1, DT2 transformatörlerinin aşırı tahmin edilen ağırlığına ve boyutlarına yol açar ve ek olarak, eşleşen kaskadın diğer varyantları ile karşılaştırıldığında, bir yerine iki transformatör gereklidir.

| IBM İÇİN PULSE GÜÇ KAYNAKLARININ TEMEL PARAMETRELERİ | Anahtarlama güç kaynaklarının ana parametreleri göz önünde bulundurulur, konektörün pin çıkışı gösterilir, 110 ve 220 voltluk şebeke voltajından çalışma prensibi, | |||

| TL494 mikro devresi, anahtarlama devresi ve anahtarlamalı güç kaynaklarının güç anahtarlarını kontrol etmek için kullanım durumları ayrıntılı olarak açıklanmaktadır. | ||||

| PULSE GÜÇ KAYNAĞININ TL494 İLE GÜÇ ANAHTARI KONTROLÜ | Darbeli güç kaynaklarının güç transistörlerinin temel devrelerini kontrol etmenin ana yöntemleri, ikincil güç kaynakları için doğrultucu oluşturma seçenekleri açıklanmaktadır. | Devre şemasının tam açıklaması ve anahtarlamalı güç kaynağının çalışması | ||